2025년 하반기 반도체 산업은 미세 공정의 물리적 한계를 극복하기 위해 단일 칩(Monolithic) 구조에서 벗어나, 서로 다른 기능을 가진 칩을 하나로 통합하는 칩렛(Chiplet) 기술로의 대전환을 맞이했습니다. SNS Insider의 최신 분석에 따르면, 글로벌 칩렛 시장 규모는 2025년 약 200억 달러(한화 약 27조 원)를 넘어섰으며, 2026년부터 연평균 73%라는 경이로운 성장률을 기록할 것으로 전망됩니다.

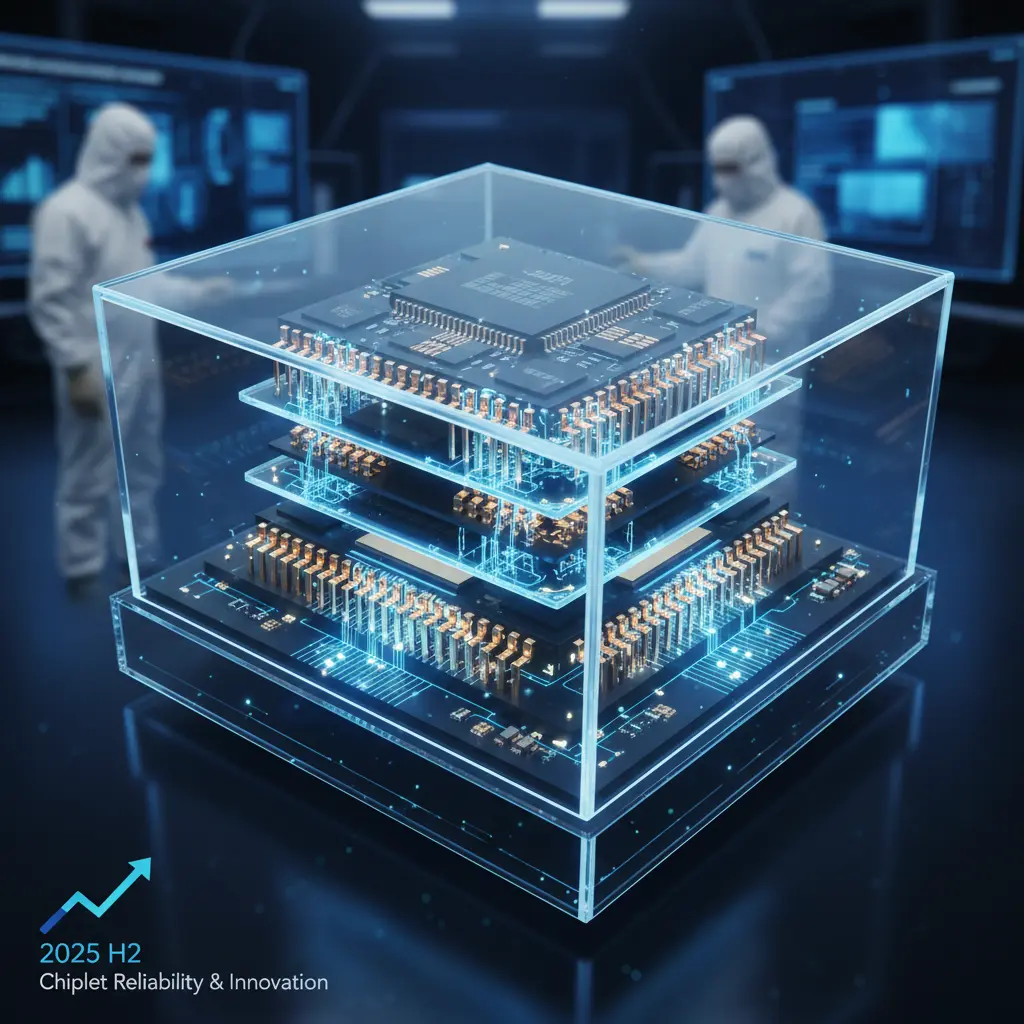

이제 반도체의 성능은 단순한 회로 선폭 경쟁을 넘어, 얼마나 정밀하게 칩을 쌓고 연결하느냐는 첨단 패키징(Advanced Packaging) 기술에 의해 결정되고 있습니다. 본 리포트에서는 칩렛 기반 이종 집적(Heterogeneous Integration) 기술의 부상과 이를 완성하는 파릴렌(Parylene)의 나노 증착 역할을 분석합니다.

1. 칩렛 아키텍처의 부상과 설계상의 난제

무어의 법칙(Moore’s Law)이 둔화되면서, 고성능 컴퓨팅(HPC)과 AI 반도체 설계자들은 수율 향상과 비용 절감을 위해 칩렛 구조를 선택하고 있습니다. 하지만 이러한 구조적 변화는 패키지 내부 설계에 새로운 도전 과제를 부여합니다.

- 초고밀도 상호 연결(Interconnects): 여러 칩렛을 연결하기 위해 실리콘 인터포저(Interposer)와 수천 개의 마이크로 범프(Micro-bump)가 사용됩니다. 이 연결 부위는 미세 오염이나 전기적 스트레스에 극도로 취약합니다.

- 열 및 기계적 스트레스 관리: 서로 다른 공정으로 제조된 칩렛들이 하나의 패키지에 묶이면서, 작동 시 발생하는 열팽창 계수(CTE) 차이로 인한 미세 균열이나 접합부 분리 현상이 발생할 위험이 커졌습니다.

- 나노 단위의 복잡한 기하 구조: 2.5D 및 3D 적층 구조가 일반화되면서 패키지 내부에는 액상 코팅제가 도저히 침투할 수 없는 10μm(마이크로미터) 수준의 좁은 틈새들이 존재하게 되었습니다.

2. 2025 하반기 패키징 트렌드: ‘완벽한 기밀 봉지’의 필수성

2025년 하반기 개최된 APCS(첨단 패키징 및 칩렛 서밋)에서는 패키지 내부의 신뢰성을 담보하기 위한 기밀 봉지(Hermetic Sealing) 기술이 핵심 화두였습니다.

특히 AI 서버용 GPU와 고대역폭 메모리(HBM)는 가혹한 고온 환경에서 작동하므로, 내부의 미세한 수분 침투나 이온 오염이 즉각적인 시스템 붕괴로 이어집니다. 이에 따라 기존 에폭시 몰딩 컴파운드(EMC)를 보완하거나, 칩과 칩 사이의 좁은 간격을 완벽히 보호할 수 있는 초박막 나노 코팅에 대한 수요가 급격히 증가했습니다.

3. 파릴렌(Parylene): 칩렛의 신뢰성을 완성하는 나노 보호막

첨단 패키징 공정에서 파릴렌은 그 독보적인 증착 특성 덕분에 칩렛 기반 이종 집적 구조의 신뢰성을 극대화하는 솔루션으로 자리 잡고 있습니다.

- 하부 침투력과 균일성: 파릴렌은 기체 상태에서 분자 단위로 증합되는 화학 기상 증착(CVD) 방식을 사용합니다. 덕분에 액체 코팅으로는 접근이 불가능한 0.01mm 미만의 좁은 틈새까지 완벽하게 침투하여, 칩 하부의 미세 공극(Crevices)을 빈틈없이 감싸는 ‘나노 재킷’ 역할을 수행합니다.

- 무응력(Stress-free) 코팅: 실온에서 형성되는 파릴렌 코팅은 열에 민감한 첨단 칩렛 소자에 기계적 스트레스를 주지 않습니다. 이는 미세한 범프 접합부의 변형을 방지하며 장기적인 물리적 안정성을 제공합니다.

- 우수한 유전 특성: 매우 낮은 유전 상수와 높은 유전 강도를 보유하여 고주파 신호 간섭을 최소화합니다. 이는 고속 데이터 전송이 필수적인 AI 반도체 패키지 내부에서 신호 무결성(Signal Integrity)을 유지하는 데 결정적인 기여를 합니다.

4. 2026년 전망 및 비즈니스 시사점

2026년은 유리 기판(Glass Substrate)과 패널 레벨 패키징(PLP) 등 차세대 패키징 폼팩터가 본격적으로 도입되는 전환점이 될 것입니다. Yole Group 및 Fortune Business Insights는 AI 반도체 수요의 약 46%가 칩렛 아키텍처에 집중될 것으로 예측합니다. 이제 반도체 패키징은 단순한 ‘포장’이 아닌, 반도체의 ‘성능과 수명’을 결정짓는 핵심 공정입니다. 나노 단위의 정밀 제어가 가능한 파릴렌 CVD 공정은 초미세 칩렛 구조 내에서 신뢰성을 검증하는 필수 표준으로 자리 잡을 것입니다. 국내외 반도체 공급망 기업들은 이러한 기술적 전환기에 맞춰 고기능성 나노 증착 기술을 적극 도입하여 수율 향상과 품질 경쟁력을 선점해야 합니다.

참고 출처 (Sources)

- SNS Insider: Chiplet Market Size, Share, Trends & Growth Report, 2033

(https://www.snsinsider.com/reports/chiplet-market-5567) - Fortune Business Insights: Chiplets Market Size, Share & Global Report [2034]

(https://www.fortunebusinessinsights.com/chiplets-market-110918) - SEMICON Japan: Advanced Packaging and Chiplet Summit (APCS) 2025 Overview

https://www.semiconjapan.org/en/apcs - SEMI: Advanced Packaging Summit 2025 – Trends in Heterogeneous Integration

https://www.semi.org/en/connect/events/advanced-packaging-summit-2025 - Advanced Coating: All About Parylene in Electronics – Crevice Penetration Benefits

(https://www.advancedcoating.com/blog/all-about-parylene-in-electronics) - 참고 출처의 링크는 출처 사이트의 사정에 따라 변경 또는 삭제될 수 있음을 알려드립니다.