2026년 상반기 반도체 산업은 역사상 가장 미세한 영역인 2나노(2nm) 공정의 양산 경쟁으로 뜨겁게 달아올랐습니다. 삼성전자와 TSMC가 주도하는 이 초미세 공정 경쟁은 단순한 선폭 축소를 넘어, 기존 핀펫(FinFET) 구조의 한계를 극복하기 위한 GAA(Gate-All-Around) 기술의 전면 도입을 알리고 있습니다.

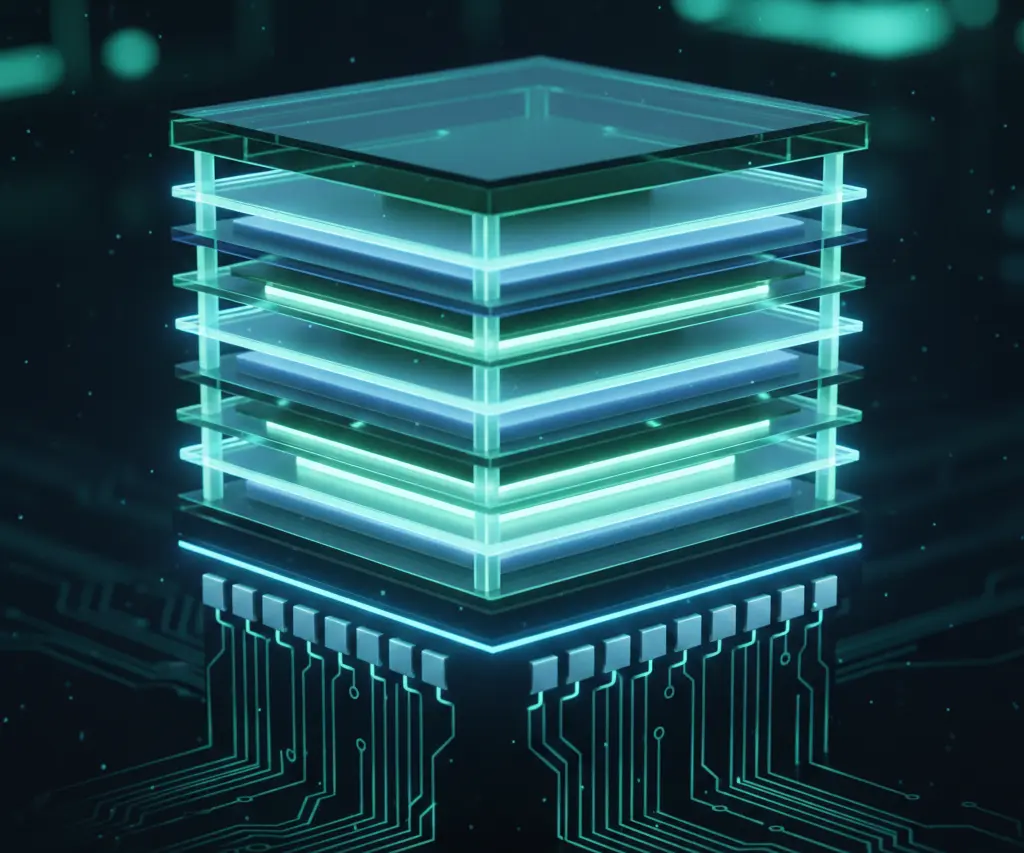

반도체 칩 내부의 게이트가 채널의 4면을 모두 감싸는 GAA 구조는 전류 제어 능력을 극대화하지만, 그만큼 공정의 난이도와 ‘신뢰성 확보’라는 새로운 임계점을 제시하고 있습니다. 본 리포트에서는 2나노 시대의 핵심 구조 변화와 이를 뒷받침하는 파릴렌(Parylene) 나노 증착 기술의 역할을 분석합니다.

1. GAAFET 아키텍처와 2나노 공정의 물리적 도전

2026년 상반기 양산이 본격화된 2나노 기반 GAAFET은 데이터 처리 속도를 높이면서도 소비 전력을 획기적으로 줄였습니다. 하지만 구조적으로는 다음과 같은 유례없는 공정 난제를 안고 있습니다.

- 나노시트(Nanosheet) 사이의 초미세 간격: 게이트와 채널이 맞닿는 면적을 넓히기 위해 적층된 나노시트 사이의 간격은 수 나노미터에 불과합니다. 이 좁은 틈새에 절연막을 균일하게 형성하지 못하면 누설 전류(Leakage Current)가 발생하여 칩 전체의 효율이 급감합니다.

- BSPDN(후면 전력 공급 네트워크)의 도입: 2나노 공정의 핵심인 BSPDN 기술은 전력 배선을 웨이퍼 후면에 배치하여 공간 효율을 높입니다. 이로 인해 칩의 전면과 후면 모두에서 극도로 얇으면서도 강력한 절연 성능을 가진 나노 박막이 필수적이 되었습니다.

- 열 밀도와 신뢰성: 좁은 공간에 수백억 개의 트랜지스터가 집적되면서 발생하는 열은 소자의 수명을 단축시킵니다. 외부 오염 물질로부터 칩을 완벽히 격리하면서도 열적 안정성을 유지하는 코팅 기술이 2나노 공정의 성공을 좌우하고 있습니다.

2. 2나노 공정의 ‘수율 파수꾼’: 파릴렌(Parylene) 나노 증착

차세대 반도체 공정에서 파릴렌은 기존 액상 코팅이나 물리적 증착이 해결하지 못한 신뢰성 문제를 해결하는 ‘나노 해결사’로 평가받습니다.

- 분자 단위의 초균일 증착: 파릴렌은 화학 기상 증착(CVD) 공정을 통해 기체 상태로 소입자 사이를 파고듭니다. GAA 구조의 복잡한 나노시트 틈새나 3D 적층 구조의 미세 공극까지 균일한 두께(Uniformity)로 도포되어, 핀홀 없는 완벽한 절연막을 형성합니다.

- BSPDN을 위한 초박막 절연 솔루션: 2나노 공정에서는 아주 미세한 부피 증가도 성능에 영향을 줍니다. 파릴렌은 수십 나노미터 수준의 초박막으로도 탁월한 유전 강도를 제공하여, BSPDN 구조에서 전력 간섭을 최소화하고 절연 신뢰성을 극대화합니다.

- 화학적 불활성 및 낮은 유전율(Low-k): 파릴렌은 증착 과정에서 화학적 부산물을 남기지 않으며, 매우 낮은 유전율을 가지고 있어 신호 전달 속도가 중요한 고성능 AI 반도체의 성능 저하를 방지합니다.

3. 2026년 상반기 시장 동향과 기술 로드맵

Gartner와 Counterpoint Research의 2026년 1분기 보고서에 따르면, AI 가속기와 고성능 서버 시장의 2나노 채택률은 예상보다 빠르게 상승하고 있습니다.

- 온디바이스 AI의 심화: 스마트폰과 웨어러블 기기에 탑재되는 2나노 AP는 가혹한 실사용 환경(온도, 습도)에서도 견뎌야 합니다. 이에 따라 칩 레벨에서의 패키징(Wafer Level Packaging) 단계에 파릴렌 코팅을 적용하여 내구성을 확보하는 사례가 늘고 있습니다.

- 글로벌 공급망 재편: 반도체 파운드리 기업들은 이제 ‘미세화’를 넘어 ‘신뢰성 공정’의 자동화를 서두르고 있습니다. 파릴렌 자동화 증착 장비의 라인 인(Line-in)은 2나노 공정 수율을 안정화하는 핵심 투자 지표가 되고 있습니다.

4. 비즈니스 시사점 및 제언

2나노 시대는 기술적 난이도가 극도로 높은 만큼, 공정 파트너사와의 협력이 중요합니다. (주)와인은 글로벌 반도체 트렌드에 발맞추어 초미세 GAA 구조에 최적화된 파릴렌 증착 레시피를 선제적으로 확보해야 합니다.

특히 2026년 하반기 예정된 3D IC와 광반도체(CPO) 시장의 확장에 대비하여, 나노 단위 제어 기술을 표준화한다면 글로벌 팹리스 및 파운드리 기업들과의 파트너십에서 독보적인 위치를 점할 수 있을 것입니다.

참고 출처 (Sources)

- Gartner: Semiconductor Market Forecast 2nm Expansion (2026.01)

(https://www.gartner.com/en/newsroom) - TSMC Official: 2nm Technology and GAA Structure Roadmap

(https://www.tsmc.com/english/dedicatedFoundry/technology/logic/l_2nm) - Samsung Newsroom: The Era of GAA – Mass Production Update 2026

(https://news.samsung.com/global/category/products/semiconductors) - TechInsights: Advanced Logic Process Analysis – 2nm and Backside Power Delivery

(https://www.techinsights.com/) - IEEE Xplore: Parylene as a Dielectric Material for Next-Generation Nanosheet FETs

(https://ieeexplore.ieee.org/)