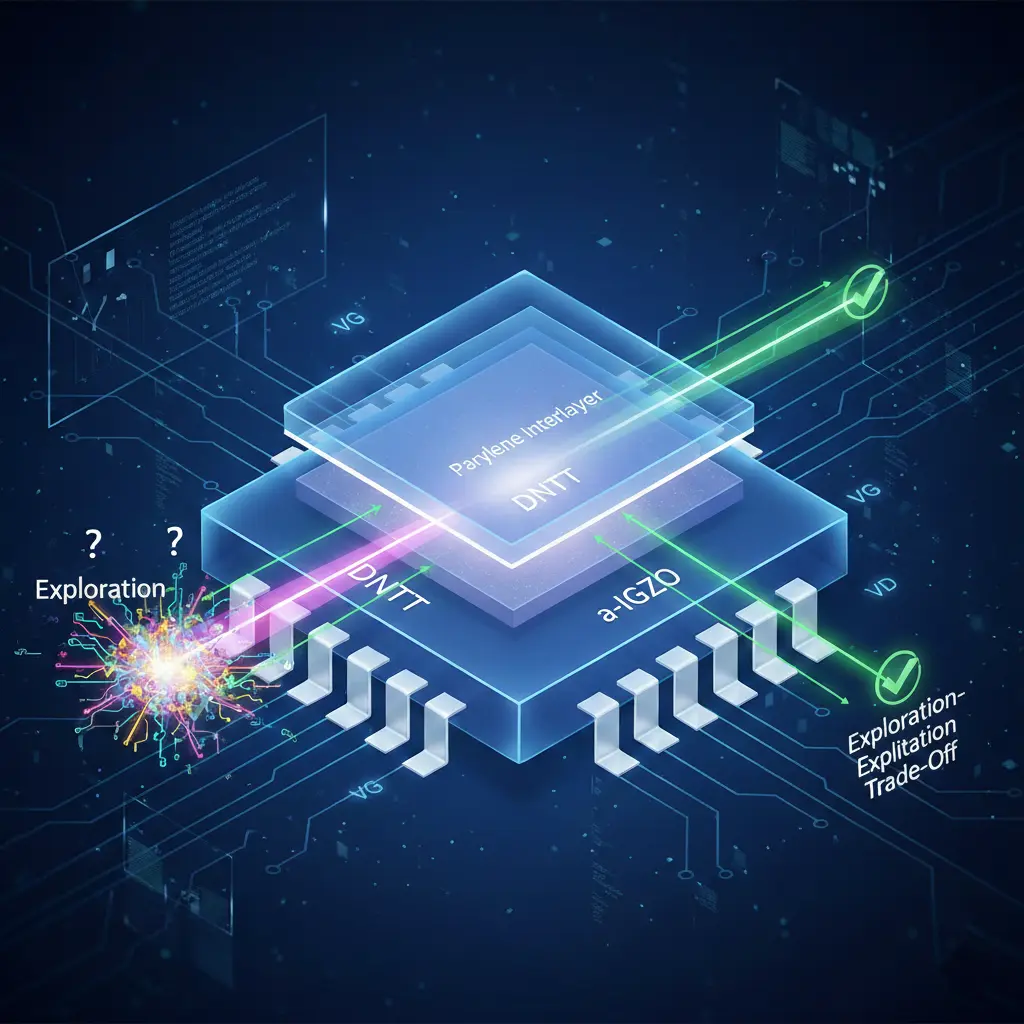

현대 인공지능 기술의 급격한 발전은 하드웨어 시스템에 전례 없는 수준의 연산 효율과 저전력 특성을 요구하고 있습니다. 특히 강화 학습(Reinforcement Learning, RL) 과정에서 발생하는 방대한 계산량과 전력 소모를 해결하기 위해 하드웨어 자체에서 수학적 활성 함수(Activation Function)를 구현하는 연구가 활발히 진행되고 있습니다. 오늘 소개해 드릴 솔루션은 차세대 뉴로모픽(Neuromorphic) 반도체 소자에서 파릴렌(Parylene) 박막을 활용하여 인공지능의 핵심 과제인 ‘탐색과 활용(Exploration-Exploitation)’의 균형을 하드웨어 수준에서 해결한 혁신적인 기술 사례입니다.

1. 개요 (Snapshot)

- 산업 분야: 차세대 인공지능 반도체 및 뉴로모픽 컴퓨팅 (Neuromorphic Computing)

- 적용 부품: 가우시안-시그모이드 강화 트랜지스터 (Gaussian-Sigmoid Reinforcement Transistor, GS-RT)

- 핵심 과제: 강화 학습 활성 함수의 하드웨어 통합 및 전력 효율 극대화

- 적용 솔루션: Parylene(diX-SR) 25nm 초박막 층간 유전체(Interlayer) 증착

- 파릴렌 종류: Parylene (diX-SR)

2. 배경 및 난제 (The Challenge)

기존의 인공지능 강화 학습(RL) 알고리즘은 가우시안(Gaussian) 함수와 시그모이드(Sigmoid) 함수를 유기적으로 사용하여 최적의 해를 찾아갑니다. 하지만 이를 실제 하드웨어로 구현할 때는 다음과 같은 심각한 기술적 한계에 직면해 왔습니다:

- 회로의 복잡성: 가우시안 및 시그모이드 활성 함수를 개별적으로 구현하기 위해서는 수십 개의 트랜지스터와 복잡한 반복 연산 회로가 필요하여 칩 면적이 커지고 설계가 복잡해지는 문제가 있었습니다.

- 높은 전력 소모: 소프트웨어 기반의 반복 연산은 막대한 전력 소모를 야기하며, 이는 실시간 데이터 처리가 필요한 엣지 컴퓨팅 기기나 자율주행 시스템 등 저전력 환경에서 치명적인 약점이 됩니다.

- 상충하는 특성 제어: 안정적인 ‘활용(Exploitation)’을 돕는 가우시안 특성과 광범위한 ‘탐색(Exploration)’을 유도하는 시그모이드 특성을 단일 소자 내에서 동적으로 전환하는 기술적 구현이 매우 어려웠습니다.

3. 기술적 요구 기준 (Technical Requirements)

차세대 뉴로모픽 소자의 성능을 확보하기 위해서는 나노미터(nm) 단위의 정밀한 박막 제어와 물리적 안정성이 필수적이었습니다:

- 초정밀 두께 제어 (Ultra-precise Thickness Control): 게이트 전계 차폐(Gate Field Screening) 효과와 전하 주입 억제 기능을 동시에 수행하기 위해 25nm 수준의 매우 얇고 균일한 두께 유지가 필수적이었습니다.

- 비침습적 계면 형성 (Non-invasive Interface): 유기 반도체(DNTT)와 산화물 반도체(a-IGZO) 사이의 물리적 손상을 최소화하면서도, 두 층 사이를 완벽하게 분리할 수 있는 화학적 안정성이 요구되었습니다.

- 표면 에너지 제어 (Surface Energy Control): 상단 유기 채널의 결정 성장을 최적화하고 소자의 신뢰성을 높이기 위해 소수성(Hydrophobic) 특성을 갖는 안정적인 표면 환경 제공이 필요했습니다.

4. 솔루션 적용 및 공정 (The Parylene Solution)

연구진은 이러한 난제를 해결하기 위한 핵심 소재로 파릴렌(Parylene, diX-SR) 기상 증착 기술을 선택했습니다. 파릴렌은 기존의 액상 코팅 방식으로는 불가능한 정밀한 적층 구조를 가능케 함으로써 소자의 기능을 완성했습니다:

- 하이브리드 특성 구현: 파릴렌 박막을 하단 게이트와 상단 DNTT 채널 사이에 정밀하게 위치시켰습니다. 이를 통해 전하 주입을 의도적으로 방해하는 ‘접촉 방해 효과(Contact Hindering Effect)’를 유도하여, 하나의 소자에서 가우시안과 시그모이드 특성이 동시에 나타나는 혼합 응답을 구현했습니다.

- 화학 기상 증착(CVD)의 이점: 복잡한 수직 적층 이종접합(Heterojunction) 구조 위에서도 단차 피복성(Step Coverage)이 뛰어난 파릴렌을 증착하여, 기포나 핀홀(Pinhole) 없는 균일한 절연층을 형성했습니다.

- 최적의 임계 두께 산출: 수많은 실험을 통해 25nm의 파릴렌 층이 게이트 필드 스크리닝을 적절히 유도하여 시그모이드 포화 성능을 극대화하는 최적의 두께임을 입증하였습니다.

5. 결과 및 기대 효과 (Key Outcomes)

파릴렌 솔루션이 적용된 GS-RT 소자는 기존 시스템 대비 압도적인 성능 향상을 실현했습니다:

- 하드웨어 간소화: 수십 개의 트랜지스터가 필요했던 활성 함수 구현 회로를 단 1개의 트랜지스터로 대체함으로써, 회로 면적을 줄이고 시스템 복잡성을 획기적으로 낮췄습니다.

- 학습 효율성 증대: 멀티 암드 밴딧(Multi-Armed Bandit) 테스트 결과, 기존 방식보다 20% 빠른 수렴 속도와 30% 높은 최종 보상(Final Reward)을 달성하여 강화 학습 효율을 극대화했습니다.

- 높은 안정성 및 견고성: 실제 카트 폴(Cart-pole) 균형 잡기 제어 과제에서 기존 ReLU 함수 기반 네트워크보다 외부 노이즈 및 입력 변동에 대해 훨씬 높은 내성을 보여주며 실용성을 증명했습니다.

6. 산업적 시사점 (Industrial Implications)

이번 사례는 파릴렌이 단순히 부품을 외부 환경으로부터 보호하는 코팅 소재를 넘어, 반도체 소자의 전기적 특성을 능동적으로 제어하고 설계하는 ‘기능성 소자 소재(Functional Electronic Material)’로서 무한한 가능성을 지니고 있음을 보여주었습니다. 이는 향후 엣지 AI 기기, 초저전력 모바일 장치 및 인간의 뇌를 모방한 차세대 뉴로모픽 플랫폼 구축에 있어 파릴렌 증착 기술이 핵심적인 국가적 경쟁력이 될 것임을 시사합니다.

7. 참고출처

Park, J.; Seo, J.; Koo, R.-H.; Jayasuriya, D.; Jayasinghe, N.; Shin, W.; Trivedi, A. R.; Yoo, H. Gaussian-Sigmoid Reinforcement Transistors: Resolving Exploration-Exploitation Trade-Off Through Gate Voltage-Controlled Activation Functions. Adv. Funct. Mater. 2025, 35, 2512407. https://doi.org/10.1002/adfm.202512407

※ 참고출처의 링크는 출처 사이트의 사정에 따라 변경 또는 삭제될 수 있음을 알려드립니다.